## Master Thesis Treball Final de Carrera

# PERFORMANCE EVALUATION OF MPEG-4 VIDEO ENCODER ON ADRES

Enric Mumbrú Bassas

#### ENGINYERIA D'ORGANITZACIÓ INDUSTRIAL

Director: Moisès Serra Serra Daily supervisor: Eric Delfosse

## **Acknowledgements**

I want to say thanks to David because he convinced me to go to Belgium and make this project. This give me the opportunity to work in one of most important research centers in microelectronics, to meet a new country and a new culture and the most important to meet new people, new friends. Thanks also to my family and friends, who support me in that important decision. Thanks also to my new friends here that I meet in Belgium for all the time spent. Finally thanks to Eric and David, again, because they helped me in my daily work.

## **Glossary**

#### **Acronyms and Abbreviations**

ADRES Architecture for Dynamically Reconfigurable Embedded Systems

CFG Control-Flow Graph

CGRA Coarse-Grained Reconfigurable Architecture

CPLD Complex Programmable Logic Device

DCT Discrete Cosine Transform

DLP Data-Level Parallelism

DPCM Differential Pulse Code Modulation

DRESC Dynamically Reconfigurable Embedded System Compiler

FPGA Field Programmable Gate Arrays

FU Functional Unit

IDCT Inverse Discrete Cosine Transform

II Initiation Interval

ILP Instruction Level Parallelism

IMEC Interuniversitary MicroElectronics Center

IMPACT Illinois Microarchitecture Project utilizing Advanced Compiler Technology

IPC Instructions Per Cycle

IR Intermediate Representation

MB MacroBlock

MC Motion Compensation

ME Motion Estimation

MPEG Motion Picture Expert Group

MRRG Modulo Routing Resource Graph

MV Motion Vector

PHP Hypertext Preprocessor

P&R Placement and Routing

RAM Random Access Memory

RF Register File

SA Simulated Annealing

SAD Sum of Absolute Differences

SD Scheduling Density

SIMD Single Instruction Multiple Data

SSA Static Single Assignment

TC Texture Coding

VLIW Very Long Instruction Word

VOP Video Object Plane

XML eXtensible Markup Language

## **Contents**

| 1 Introduction                                  | 1  |

|-------------------------------------------------|----|

| 2 ADRES an architecture template                | 2  |

| 2.1 Introduction                                | 2  |

| 2.2 Architecture Template Description           | 3  |

| 2.2.1 Execution and Configuration Model         | 6  |

| 2.2.2 Functional Units                          | 6  |

| 2.2.3 Register Files                            | 7  |

| 2.2.4 Routing Networks                          | 7  |

| 2.3 XML-Based Architecture Description Flow     | 7  |

| 2.4 ADRES compiler: DRESC                       | 9  |

| 2.4.1 The structure of DRESC compiler           | 9  |

| 2.4.2 Program Analysis and Transformation       | 10 |

| 2.4.3 Modulo scheduling                         | 12 |

| 3 Source-Level Transformations                  | 14 |

| 3.1 Constraint-Removing Transformations         | 14 |

| 3.2 Performance-Enhancing Transformations       | 15 |

| 3.3 Guidelines for Source-Level Transformations | 18 |

| 4 MPEG-4                                        | 20 |

| 4.1 MPEG-4 standard                             | 20 |

| 4.2 MPEG-4 encoder description                  | 22 |

| 4.3 Code mapped                                 | 23 |

| 5 Texture Coding                                | 25 |

| 5.1 Introduction                                | 25 |

| 5.2 Block Level                                 | 26 |

| 5.2.1 Quantization/DeQuantization function      | 27 |

| 5.2.2 IDCT_cols function                        | 30 |

| 5.2.3 IDCT_rows function                        | 30 |

| 5.3 MacroBlock Level                            | 31 |

| 5.4 Block Type 1                                | 35 |

| 5.5 Comparison between block and MB levels      | 36 |

| 6 Motion Estimation                             | 39 |

#### CONTENTS

| 6.1     | Motion Estimation description process                                                          | 39 |

|---------|------------------------------------------------------------------------------------------------|----|

| 6.2     | Code transformations                                                                           | 41 |

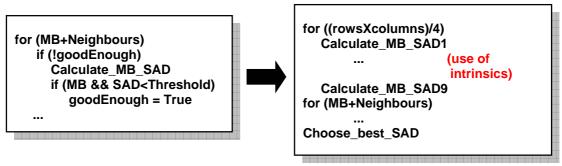

| 6.2.1   | Calculate INTER – MB SAD                                                                       | 42 |

| 6.2.2   | Calculate INTRA – MB SAD                                                                       | 43 |

| 6.2.3   | Choose Mode                                                                                    | 43 |

| 6.2.4   | Full – Pixel Motion Estimation                                                                 | 45 |

| 6.2.5   | Half – Pixel Motion Estimation                                                                 | 45 |

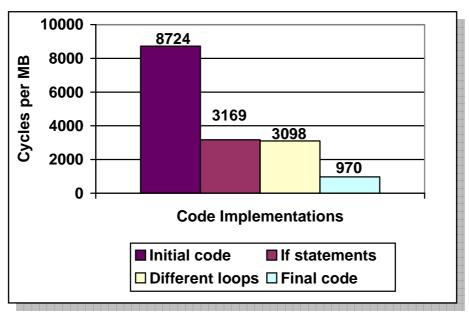

| 6.3     | General statistics                                                                             | 48 |

| 7 Te    | exture Update                                                                                  | 50 |

| 7.1     | Initial code                                                                                   | 50 |

| 7.2     | Final code                                                                                     | 51 |

| 7.3     | General statistics                                                                             |    |

| 8 Mc    | otion Compensation                                                                             | 56 |

| 8.1     | Initial code                                                                                   |    |

| 8.2     | Final Code                                                                                     | 58 |

| 8.3     | General statistics                                                                             | 62 |

| 9 Cc    | onclusions and future work                                                                     |    |

| 9.1     | Results achieved                                                                               | 64 |

| 9.2     | Code analysis                                                                                  |    |

| 9.3     | About ADRES and its compiler                                                                   |    |

| 9.4     | Future work                                                                                    |    |

| Lis     | st of Tables                                                                                   |    |

| Figure  | e 1 ADRES in relation to other architectures                                                   | 3  |

| Figure  | e 2: The ADRES system                                                                          | 3  |

| •       | e 3 an instance of the ADRES array                                                             |    |

|         | e 4 an example of detailed datapath                                                            |    |

| •       | e 5 The functional unit in ADRES                                                               |    |

|         | e 6 The architecture description flow of the ADRES template                                    |    |

| •       | e 7 structure of DRESC compilere 8 The flow of transformation, analysis and optimization steps |    |

| •       | e 9 The modulo scheduling algorithm core                                                       |    |

| · iguit | 5 0 1110 1110 and dollowalling digoritimi dolo                                                 |    |

#### CONTENTS

| Figure 10 | Transformations for an IDCT loop                                             | 15 |

|-----------|------------------------------------------------------------------------------|----|

| Figure 11 | Example of loop coalescing                                                   | 16 |

| Figure 12 | Example of loop unrolling                                                    | 17 |

| Figure 13 | Example of tree height reduction                                             | 18 |

| Figure 14 | Encoder data flow                                                            | 22 |

| Figure 15 | Texture Coding flowchart                                                     | 26 |

| Figure 16 | Initial and final schematic block level code                                 | 27 |

| Figure 17 | DRESC_Q_invQ original schematic disposition                                  | 28 |

| Figure 18 | Schematic code in block and macroblock level                                 | 31 |

| Figure 19 | Changes in memory accesses                                                   | 32 |

| Figure 20 | Different options to read from the memory: short type (left) or integer type |    |

| (right)   |                                                                              | 32 |

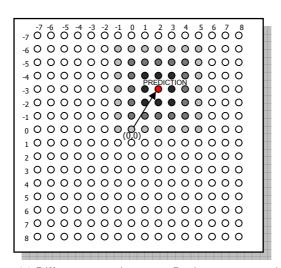

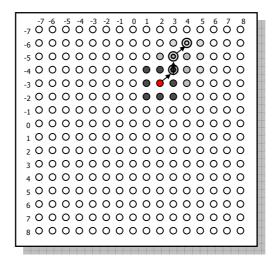

| Figure 21 | Different search zones. Darkest are search first                             | 40 |

| Figure 22 | Checking points process                                                      | 41 |

| Figure 23 | Code transformations in INTER-MB SAD                                         | 42 |

| Figure 24 | Code transformations in INTRA-MB SAD                                         | 43 |

| Figure 25 | Code transformations in ChooseMode function                                  | 44 |

| Figure 26 | Code transformations in Full-Pel ME                                          | 45 |

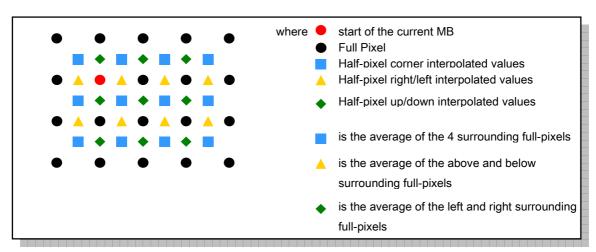

| Figure 27 | Half-pixel types                                                             | 46 |

| Figure 28 | Code transformations in Half-Pel ME                                          | 47 |

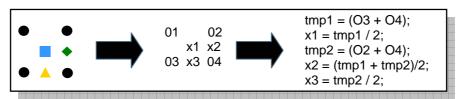

| Figure 29 | Scheme of interpolation value using previous calculated values               | 47 |

| Figure 30 | Schematic initial code in Texture Update block                               | 51 |

| Figure 31 | Schematic blocktype selection process                                        | 52 |

| Figure 32 | Main loop in Texture Update                                                  | 53 |

| Figure 33 | Motion Compensation schematic code                                           | 57 |

| Figure 34 | Final schematic code for Y-blocks                                            | 59 |

| Figure 35 | Final schematic code for UV blocks                                           | 60 |

| Figure 36 | Total cycles coalescing or not coalescing loops                              | 66 |

| Figure 37 | intrinsic process to make interpolation in Half-Pixel ME                     | 69 |

| Figure 38 | Intrinsic code in Half-Pixel Motion Estimation                               | 70 |

| Figure 39 | Intrinsic process in MC                                                      | 71 |

| Figure 40 | Motion Compensation Intrinsic Code                                           | 71 |

| Figure 41 | Intrinsic process for TU block                                               | 72 |

| Figure 42 | Texture Update Intrinsic Code                                                | 73 |

|           |                                                                              |    |

## **List of Tables**

| Table 1 Scheduling results for DCT                                      | 27 |

|-------------------------------------------------------------------------|----|

| Table 2 Scheduling results for different Q_invQ options                 | 29 |

| Table 3 IDCT_cols scheduling results                                    | 30 |

| Table 4 IDCT_rows scheduling results                                    | 31 |

| Table 5 Scheduling results for different options to read at memory      | 32 |

| Table 6 Scheduling results for DCT_Cols in MB level                     | 33 |

| Table 7 Q_invQ scheduling results in Mb level                           | 34 |

| Table 8 Different scheduling results for IDCT_Cols in MB level          | 34 |

| Table 9 IDCT_Rows scheduling results obtained in MB level               | 35 |

| Table 10 BlockDirDCTQuantH263 scheduling results                        | 35 |

| Table 11 BlockDirDequantH263IDCT scheduling results                     | 36 |

| Table 12 Block and MB level statistics (Q_invQ in block level)          | 36 |

| Table 13 INTER-MB SAD schedule results                                  | 42 |

| Table 14 INTRA-MB SAD schedule results                                  | 43 |

| Table 15 ChooseMode schedule results                                    | 44 |

| Table 16 Scheduling results for Full-Pel ME                             | 45 |

| Table 17 Half-Pel ME schedule results                                   | 48 |

| Table 18 Scheduling results for Texture Update block                    | 53 |

| Table 19 Motion Compensation scheduling results                         | 61 |

| List of Graphics                                                        |    |

| Orachia 4 Origa Origania antatian manulta                               | 00 |

| Graphic 1 Q_invQ implementation results                                 |    |

| Graphic 2 Q_invQ Implementations in MB Level                            |    |

| Graphic 3 CGA Cycles comparison between block and MB levels             |    |

| Graphic 4 CGA mode and VLIW mode results                                |    |

| Graphic 5 Total cycles for different option tested in Half-Pel ME       |    |

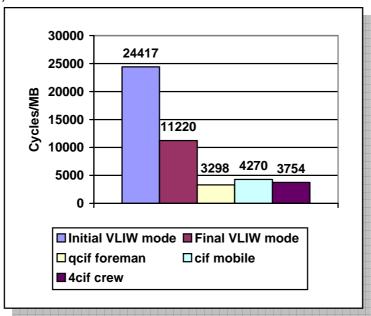

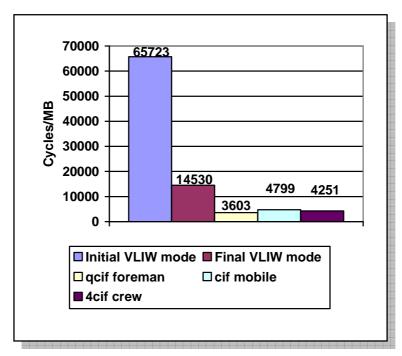

| Graphic 6 ME comparison between different sequences and CGA/VLIW modes  |    |

| Graphic 7 Comparison between different options tested                   |    |

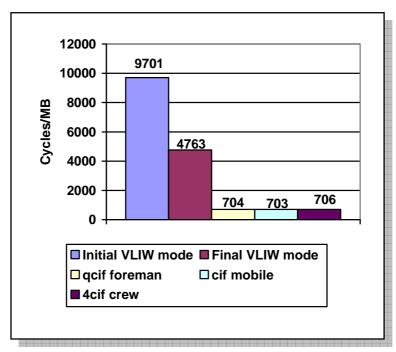

| Graphic 8 TU comparison between different sequences and CGA/VLIW modes  |    |

| Graphic 9 Comparison between different options tested                   |    |

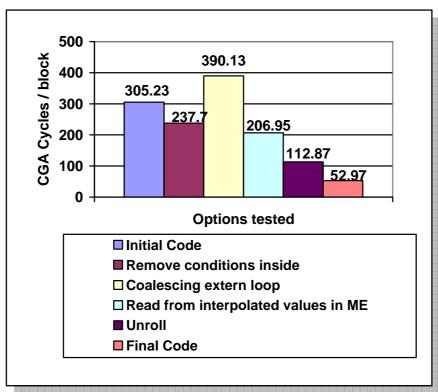

| Graphic 10 MC comparison between different sequences and CGA/VLIW modes | 62 |

#### Chapter 1

### Introduction

Nowadays, a typical embedded system requires high performance to perform tasks such as video encoding/decoding at run-time. It should consume little energy to work hours or even days using a lightweight battery. It should be flexible enough to integrate multiple applications and standards in one single device. It has to be designed and verified in short time-to-market despite substantially increased complexity. The designers are struggling to meet these huge challenges, which call for innovations of both architectures and design methodology.

Coarse-grained reconfigurable architectures (CGRAs) are emerging as potential candidates to meet the above challenges. Many of them were proposed in recent years. These architectures often consist of tens to hundreds of functional units (FUs), which are capable of executing word-level operations instead of bit-level ones found in common Field Programmable Gate Arrays (FPGAs). This coarse granularity greatly reduces delay, area, power and configuration time compared with FPGAs. On the other hand, compared with traditional "coarse-grained" programmable processors, their massive computational resources enable them to achieve high parallelism and efficiency. However, existing CGRAs have yet been widely adopted mainly because of programming difficulty for such complex architecture.

ADRES is a novel CGRA designed by Interuniversity Micro-Electronics Center (IMEC). It tightly couples a very-long instruction word (VLIW) processor and a coarse-grained array by providing two functional views on the same physical resources. It brings advantages such as high performance, low communication overhead and easiness of programming. Finally, ADRES is a template instead of a concrete architecture. With the retargetable compilation support from DRESC (Dynamically Reconfigurable Embedded System Compile), architectural exploration becomes possible to discover better architectures or design domain-specific architectures.

In this thesis, a performance of an MPEG-4 encoder in ADRES is presented. The thesis shows the code evolution to obtain a good implementation for a given architecture. Additionally the main features of ADRES and its compiler (DRESC) are presented.

The thesis is organized as follows: firstly ADRES architecture is presented and compared with other current architectures. Then the principal characteristics of DRESC compiler, the design flowchart and some other necessary background are explained. The necessary requisites for mapping loops properly in the CGA are explained as well. Brief overviews of the MPEG-4 standard and MPEG-4 encoder are given. Finally the different code transformations, code issues and results are presented.

#### Chapter 2

## **ADRES** an architecture template

#### 2.1 Introduction

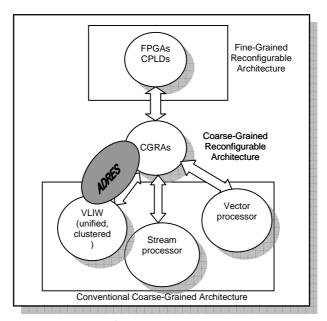

Coarse-grained reconfigurable architectures (CGRAs) [1] are emerging technology that has been deeply influenced by some existing architectures, including FPGAs (Field Programmable Gate Arrays) [2] and VLIW (Very Long Instruction Word) processors [3]. Because CGRAs are highly parallel architectures, they are also similar with other parallel computing architectures like vector processors. Moreover, the ADRES architecture combines features of both CGRA and VLIW processors and borrows many techniques from processor compilation. To fully understand ADRES and its compilation techniques, it is necessary know all the related areas. Figure 1 shows the relations between CGRAs and other architectures, as well as the position of the ADRES architecture in relation to these architectures. CGRAs partly originated from fine-grained reconfigurable architectures represented by FPGAs. Basically, at the top-level they look very similar. Both comprise an array of basic units, configurable logic blocks for FPGAs and functional units for CGRAs. Both are connected by reconfigurable routing networks. The functionality of a target application can be implemented by specializing both the basic units and the routing networks. Both are highly parallel architectures that enable exploitation of massive parallelism. The limited routing resources impose great design challenges on both architectures as well.

Much coarse-grained reconfigurable architecture (CGRA) has been developed in recent years. These architectures provide potential vehicles for future embedded system design. However, they still present many challenging issues, especially in how to support an efficient and automated design methodology. To attack these issues, the solution has to come from close interplay between both the architecture and design methodology developments.

Figure 1 ADRES in relation to other architectures

#### 2.2 Architecture Template Description

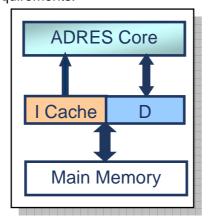

describes the system view of the ADRES architecture [4]. It is similar to a processor with an execution core attached to a memory hierarchy. Though architectural details at this moment are not well defined yet, we assume an ADRES array is connected to both data and instruction caches. At the next level, the caches are connected to a unified main memory. Though we assume two levels of memory hierarchy, more levels are possible, depending on application requirements.

Figure 2: The ADRES system

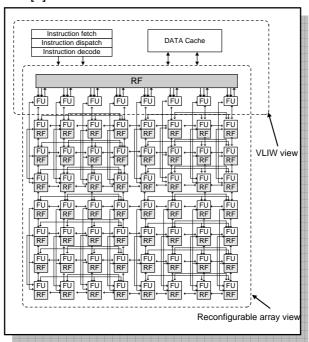

Inside the ADRES array (Figure 3), we find many basic components, including computational resources, storage resources and routing resources. The computational resources are functional units (FUs), which are capable of executing a set of operations.

#### CHAPTER 2: ADRES AN ARCHITECTURE TEMPLATE

The storage resources mainly refer to the register file (RFs) and memory blocks, which can store intermediate data. Currently, only the RFs are supported by the compiler. The routing resources include wires, multiplexers and busses. Basically, computational resources and storage resources are connected by the routing resources in the ADRES array. This is similar to other CGRAs. The ADRES array is a flexible template instead of

#### a concrete instance.

Figure 3 only shows one instance of the ADRES array with a topology resembling the MorphoSys architecture [8].

Figure 3 an instance of the ADRES array

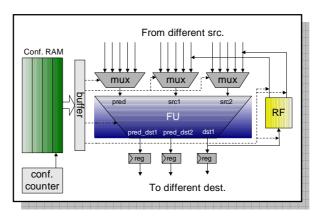

Figure 4 shows an example of the detailed datapath. The FU performs coarse grained operations. To remove the control flow inside loops, the FU supports predicated operations. To guarantee timing, the outputs of FUs are required to be buffered by an output register. The results of the FU can be written to the RF, which is usually small and has fewer ports than the shared RF, or routed to other FUs. The multiplexers are used for routing data from different sources. The configuration Random Access Memory (RAM) provides bits to control these components. It stores a number of configuration contexts locally, which can be loaded on a cycle-by-cycle basis. The configurations can also be loaded from the memory hierarchy at the cost of extra delay if the local configuration RAM is not big enough.

Figure 4 shows only one possibility of how the datapath can be constructed. Very different instances are possible. For example, the output ports of a RF can be connected to input ports of several neighboring FUs. The ADRES template has much freedom to build an instance out of these basic components.

Figure 4 an example of detailed datapath

The most important feature of the ADRES architecture is the tight coupling between a VLIW processor and a coarse-grained reconfigurable array. Since the VLIW processor and CGRAs use similar components like FUs and RFs, a natural thought is to make them share those components though the FUs and RFs in the VLIW are typically more complex and powerful. The whole ADRES architecture has two virtual functional views: a VLIW processor and a reconfigurable array. These two virtual views share some physical resources because their executions will never overlap with each other thanks to the processor/coprocessor execution model. For the VLIW processor, several FUs are allocated and connected together through one multi-port register file. The FUs used in VLIW are generally more powerful. For example, some of them have to support the branch and subroutine call operations. Additionally, only these FUs are connected to the main memory hierarchy at this moment, depending on available ports. The instructions of the VLIW processor are loaded from the main instruction memory hierarchy. This requires typical steps like instruction fetching, dispatching and decoding. For the reconfigurable array part, all the resources, including the RF and FUs of the VLIW processor, form a big 2D array. The array is connected by partial routing resources. Dataflow like kernels are mapped to the array in a pipelined way to exploit high parallelism. The FUs and RFs of the array are simpler than those of the VLIW processor. The communication between these two virtual views is through the shared VLIW register file and memory access. The sharing is in the time dimension so that it does not increase the hardware cost. For example, it does not require more ports in the VLIW RF.

#### 2.2.1 Execution and Configuration Model

There are two execution modes, VLIW mode and array mode, for the ADRES architecture. These two modes work mutually exclusive and take advantage of the tight coupling of the architecture. The VLIW mode executes the code that can not be

pipelined but mapped effectively in an ILP way, while the array mode executes kernels pipelined on the entire array. The control is transferred between these two modes by detecting entry and exit conditions of pipelined loops.

In the VLIW mode, the configuration is performed as in all other VLIW processors; in each cycle, an instruction is fetched and executed in each cycle from the instruction memory hierarchy. In the array mode, the configuration contexts are fetched from the on-chip configuration memory. Each kernel may use one or more consecutive contexts.

#### 2.2.2 Functional Units

An FU can perform a set of operations. In ADRES, only fixed-point operations are supported because they are considered sufficient for typical telecommunication and multimedia applications. The instruction set used in ADRES is constrained by the compiler front-end, i.e., the IMPACT framework. All FUs are fully pipelined so that one instruction can be issued at each cycle even when the latency of that instruction is bigger than one cycle. Different implementations may lead to different latency, which can be specified in the architecture description and is supported by the compiler.

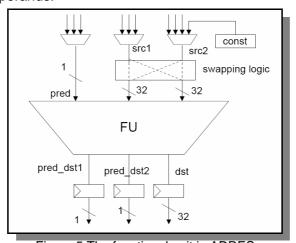

Unlike with most other CGRAs, predicated execution is introduced in the FUs in order to remove control-flow and do other transformations. Figure 5 shows the general picture of an FU. Basically, it has three source operands: pred, src1 and src2. pred is a 1-bit signal. If it is 1, the operation is executed; otherwise, the operation is nullified. src1 and src2 are normal data source operands.

Figure 5 The functional unit in ADRES

Some operations may only use one of them. The operation set comprises several groups: arithmetic, logic, shift memory, comparison and operations that generate predicates.

#### 2.2.3 Register Files

The register files (RFs) are used to store temporary data. There are two types of RFs: predicate and data RFs. The predicate RFs are 1-bit to store the predicate signal and the data RFs have the same data width as FUs. The modulo scheduling used for pipelining kernels imposes special requirements on the register file.

The modulo scheduling used for pipelining kernels imposes special requirements on the register le. In the pipelined loops, different iterations are overlapped. Therefore, the lifetime of the same variable may overlap over different iterations. To accommodate this situation, each of the simultaneously live instances needs its own register. Furthermore, the name of the used register has to be clearly identified, either in software or in hardware.

#### 2.2.4 Routing Networks

The routing networks consist of a data network and a predicate network. The data network routes the normal data among FUs and RFs, while the predicate network directs 1-bit predicate signals. These two networks do not necessarily have the same topology and can not overlap because of different data widths. Apart from its main purpose of handling control-flow, the predicate signal together with its routing network also serves for other purposes: eliminating prologue and epilogue; controlling the WE (write enable port) of the VLIW register file.

#### 2.3 XML-Based Architecture Description Flow

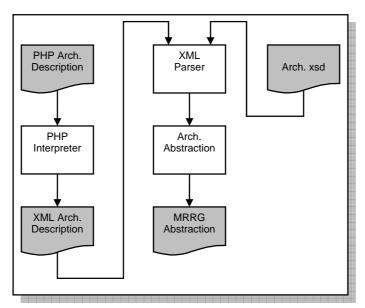

To describe an architecture instance within the vast space of the ADRES template, it uses an architecture flow based on both Extensible Markup Language (XML) and Hypertext Preprocessor (PHP) languages (Figure 6).

Figure 6 The architecture description flow of the ADRES template

XML is a simple, very flexible text format. It is designed to describe and deliver structured documents over the Internet. Unlike other markup languages such as HyperText Markup Language (HTML), its tags and semantics are not predefined. Therefore, XML is a kind of meta-language. A new language can be easily derived from XML by defining tags and structural relationships between them. Since XML is widely used in Internet context, several implementations of XML parsers are readily available in the form of open-source libraries. These libraries can be linked into the target applications and provide built-in parsing capability.

The overall architecture description comprises four sections: resource, connection, behavior and component. The resource section allocates a number of resources of different types.

The resources include FUs, RFs and TRNs (transitory nodes). For FU, the names of input and output ports, data width and supported operation groups can be specified. For FU, the names of input and output ports, data width and supported operation groups can be specified. The operation groups themselves are defined in the behavior section. RFs are specified in a similar way.

The connection section defines the topology of an ADRES instance. The behavior section defines some other architectural properties. For example, it specifies which RF is used as the one of the VLIW processor, how operations are grouped and the latency of each operation group. The area models of other components like FUs and RFs are integrated into the resource section for implementation convenience. Finally, the component section currently specifies area models of multiplexers so that the DRESC

framework can quickly estimate the area required for the interconnection for a given ADRES instance.

#### 2.4 ADRES compiler: DRESC

#### 2.4.1 The structure of DRESC compiler

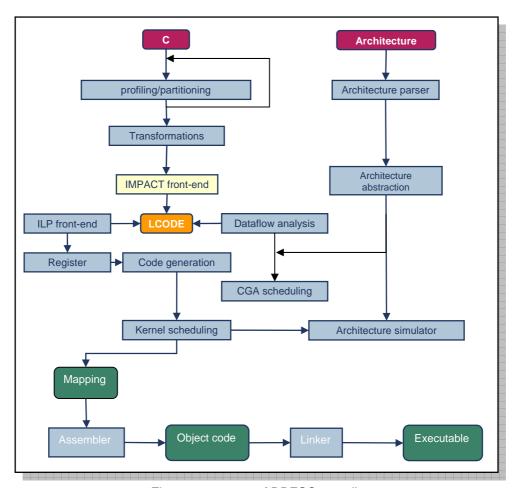

Figure 7 shows the overall structure of DRESC compiler [5]. DRESC is supported on IMPACT compiler framework [6] as a front-end to parse C source code, do some optimization and analysis, construct the required hyperblock [[11], and emit the intermediate representation (IR), which is called *lcode*. Moreover, IMPACT is also used as a library in DRESC implementation to parse *lcode*, on the basis of which DRESC's own internal representation is constructed.

Figure 7 structure of DRESC compiler

#### CHAPTER 2: ADRES AN ARCHITECTURE TEMPLATE

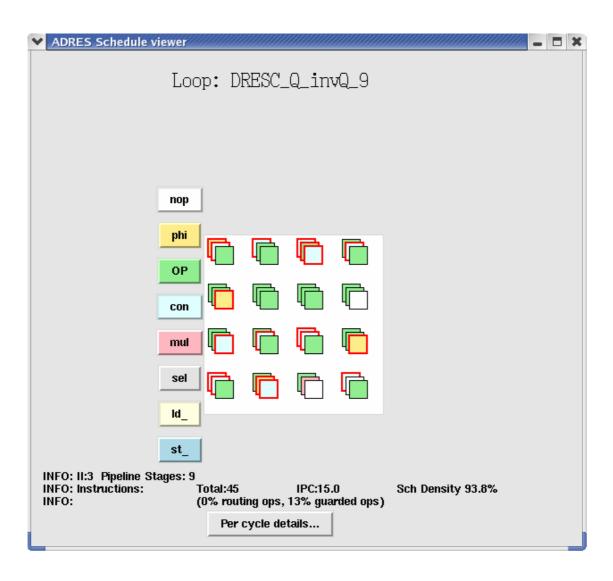

Taking lcode as input, various analysis passes are executed to obtain necessary information for later transformation and scheduling, for instance, pipelinable loops are identified and predicate-sensitive dataflow analysis is performed to construct a data dependency graph (DDG). Next, a number of program transformations are performed to build a scheduling-ready pure dataflow used by the scheduling phase. Since the target reconfigurable architectures are different from traditional processors, some new techniques are developed, while others are mostly borrowed from VLIW compilation domain. In the right-hand side of Figure 7, the architecture description and abstraction path is shown. An architecture parser translates the description to an internal architecture description format. From this internal format, an architecture abstraction step generates a modulo routing resource graph (MRRG) which is used by the modulo scheduling algorithm. The modulo scheduling algorithm plays a central role in the DRESC compiler because the major strength of coarse-grained reconfigurable architectures is in loop-level parallelism. At this point, both program and architecture are represented in the forms of graphs. The task of modulo scheduling is to map the program graph to the architecture graph and try to achieve optimal performance while respecting all dependencies. After that, the scheduled code is fed to a simulator.

#### **2.4.2** Program Analysis and Transformation

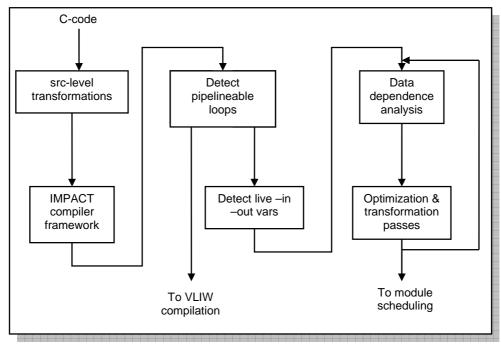

The array part of the ADRES architecture relies on loop pipelining to achieve high parallelism. Consequently, the techniques to extract and prepare properly loops are essential to the whole DRESC compiler framework. The flow of these steps is shown in Figure 8.

Figure 8 The flow of transformation, analysis and optimization steps

First, source-level transformations are applied to the application, currently based on manual C-to-C rewriting. This step tries to prepare pipelineable loops since the original source code may not be written in a pipelining-friendly way. Next the IMPACT compiler framework parses the C code, does its own analysis and optimization steps, which are designed for VLIW compilation, and emits an assembly-based intermediate representation, Lcode. Taking Lcode as input, the data-flow analysis implemented in DRESC includes detection of pipelineable loops, detection of live-in and live-out variables, and data dependence analysis. These steps generate data dependence graphs (DDG) representing the loop bodies and relevant information. However, they still cannot be directly scheduled on the ADRES architecture. For example, to reduce configuration overhead the prologue and epilogue should be properly handled in order to obtain the kernel-only code. Hence, some new optimization and transformation techniques are developed. Each transformation or optimization pass is followed repeatedly by the data dependence analysis step to update the DDG. Finally, the analyzed and optimized DDGs are fed to the modulo scheduler to exploit parallelism. The principal steps are:

- Identifying Pipelinable Loops.

- Data Dependence Graph Construction.

- Normalized Static Single Assignment Form (SSA).

- Live-in and Live-out Analysis

- Removing Explicit Prologue and Epilogue.

#### CHAPTER 2: ADRES AN ARCHITECTURE TEMPLATE

- Calculation of Minimum Initiation Interval (MII).

- Operation Ordering.

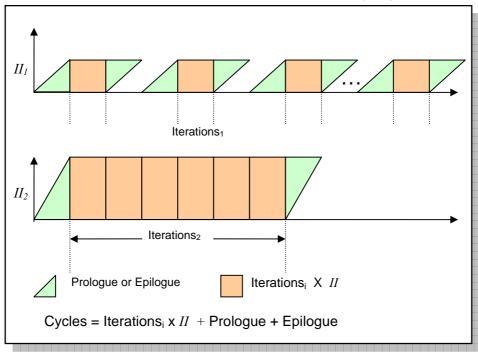

#### 2.4.3 Modulo scheduling

Modulo scheduling is one of many software pipelining techniques [7]. Its objective is to engineer a schedule for one iteration of the loop such that this same schedule is repeated at regular intervals with respect to intra- or inter-iteration dependency and resource constraints. This interval is termed the *initiation interval* (II), essentially reflecting the performance of the scheduled loop. Various effective heuristics have been developed to attack this problem for both unified and clustered VLIW. However, they can't be applied to the case of a coarse-grained reconfigurable matrix because the nature of the problem becomes more difficult.

For unified VLIW, scheduling means to decide *when* to place operation. For clustered VLIW, we also have to decide *where* to assign the operation, this is a placement problem. For coarse-grained reconfigurable architecture, there is one additional task: determining *how* to connect placed operations. This is essentially a routing problem. If we view time as one dimension of P&R space, the scheduling can be defined as a P&R problem in 3D space, where routing resources are asymmetric and modulo constraints are applied.

This scheduling problem is more complex, especially if the nature of P&R space and scarce routing resources are considered. In FPGA's P&R algorithms, it is easy to run the placement algorithm first by minimizing a good cost function that measures the quality of placement. After the minimal cost is reached, the scheduling algorithm connects placed nodes. The coupling between these two sub-problems is very loose. In ADRES, it is difficult to separate placement and routing as two independent problems. It is almost impossible to find a placement algorithm and cost function which cans force the routability during the routing phase. The solution applied in ADRES is to solve these two sub-problems in one framework.

The algorithm is described in Figure 9. Like other modulo scheduling algorithms, the outermost loop tries successively larger II, starting with an initial value equal to MII, until the loop has been scheduled. For each II, it first generates an initial schedule which respects dependency constraints, but may overuse resources. For example, more than one operation may be scheduled on one FU at the same cycle.

In the inner loop, the algorithm iteratively reduces resource overuse and tries to come up with a legal schedule. At every iteration, an operation is ripped up from the existing schedule, and is placed randomly. The connected nets are rerouted accordingly. Then a cost function is computed to evaluate the new placement and routing. A *simulated* annealing strategy is used to decide whether we accept the new placement or not. If the

new cost is smaller than the old one, the new P&R of this operation will be accepted. Even if the new cost is bigger, there is still a chance to accept the move, depending on "temperature". This method helps to escape from local minimum.

The temperature is gradually decreased from a high value. So the operation is increasingly difficult to move. The cost function is constructed by taking account into overused resources. The penalty associated with them is increased every iteration. In this way, placer and router would try to find alternatives to avoid congestion. This idea is borrowed from the *Pathfinder* algorithm. In the end, if the algorithm runs out of time budget without finding a valid schedule, it starts with the next II. This algorithm is time-consuming. It takes minutes to schedule a loop of medium size.

```

II := MII;

while not scheduled do

InitMrrg(II);

InitTemperature();

InitPlaceAndRoute():

while not scheduled do

for each op in sorted operation list

RipUpOp();

for i := 1 to random_pos_to_try do

pos := GenRandomPos();

success := PlaceAndRouteOp(pos);

if success then

new_cost := ComputeCost(op);

accepted := EvaluateNewPos();

if accepted then

break;

else

continue;

endif

endfor

if not accepted then

RestoreOp();

else

CommitOp();

if get a valid schedule then

return scheduled:

endfor

if run out of time budget then

break;

UpdateOverusePenalty();

UpdateTemperature();

endwhile

11++;

endwhile

```

Figure 9 The modulo scheduling algorithm core

#### **Chapter 3**

## **Source-Level Transformations**

Since applications written in C language are often intended for software implementation, their loops may not be appropriate for pipelining. Therefore, some source-level transformations techniques are needed to prepare proper loops for mapping on the ADRES array [4]. Generally, there are two types of transformations. One type is to remove constraints for pipelining because a loop is pipelineable only if it meets some strict requirements. For example, it cannot contain function calls inside the loop body and cannot jump out in the middle of the loop body. To meet these requirements, techniques such as function inlining have to be applied to make code pipelineable. The other type of transformations helps to improve performance because a loop may not produce good performance in its original form though it is pipelineable. For example, if there are too few iterations in the loop, loop coalescing can be used to increase total iterations by combining nested loops.

#### 3.1 Constraint-Removing Transformations

A loop is pipelineable only if it meets the following conditions:

- The loop body does not contain control-flow unless if-conversion can be applied.

- The loop body does not contain function calls.

- The loop body does not contain exit points other than the one at the end of the loop body.

Removing Control-flow and Early Exit: The control-flow and the multiple exit points are partly addressed by aggressive hyperblock formation. Nonetheless, the automatic compilation technique sometimes cannot figure out how to deal with control-flow that requires application-specific knowledge. Figure 10 shows an IDCT (inverse discrete cosine transform) example from the MPEG-2 decoder. The original source code is optimized for a traditional processor. There is a piece of shortcut code that tries to identify a special case and jump out the loop early. This piece of code is not pipelineable on the ADRES array. Therefore, it is removed by source-level transformation.

```

for (i=0; i< 8; i++)

short block[12][64];

idctrow(block + 8*i);

for (i=0; i<8 * block count; i++){

void idctrow(short *blk)

n = i / 8; /* n is block no. */

m = i \% 8; /* m is row no. */

if (!((x1 = blk[4] << 11) | (x2 = blk[6]) |...)

blk = block[n] + 8 * m;

...)

{ /*shorcut */ }

x0 = (blk[0] << 11) + 128;

x1 = blk[4] << 11;

x0 = (blk[0] << 11) + 128

x8 = W7*(x4+x5);)>>8;

blk[6] = (x3-x2) >> 8;

blk[7] = (x7-x1)>>8;

blk[6] = (x3-x2) >> 8;

blk[7] = (x7-x1) >> 8;

}

```

Figure 10 Transformations for an IDCT loop

**Function inlining** is a widely used optimization technique to reduce the overhead associated with function calls. However, it comes at the expense of increased code size if the inlined function is called in multiple places. Applied to the ADRES architecture, its primary purpose is to make loop pipelining feasible because the function call is not allowed inside a pipelineable loop. In Figure 10, the original loop includes a function idctrow, which performs 1D-IDCT on a row of pixels. After transformation, this function is inlined in the loop body to enable the pipelining.

#### 3.2 Performance-Enhancing Transformations

Loop Coalescing: Currently the DRESC compiler can only pipeline the innermost loop of a nested loop. If the outer loops contribute to a significant portion of total execution time, or the total number of iterations of the innermost loops is too small so that the overhead of prologue and epilogue is dominant, only pipelining the innermost loops won't produce good performance according to Amdahl's law. One technique that helps to solve this problem is loop coalescing. Coalescing combines a loop nest into a single loop, with the original indices computed from the resulting single induction variable. Figure 11 describes an example. This transformation is originally developed for multiprocessor-based parallel computing. It can effectively increase the significance of the innermost loop though at the cost of recomputing the indices. Normally, coalescing two innermost loops should be sufficient to form a significant innermost loop for pipelining while still keeping the overhead low.

```

for( i = 0; i < n; i++){

for( j = 0; j < m; j++){

a[i,j] = a[i,j] + c;

}

}

for (t = 0; t < n*m; t++){

i = t/m;

j = t%m;

a[i,j] = a[i,j] + c;

}

```

Figure 11 Example of loop coalescing

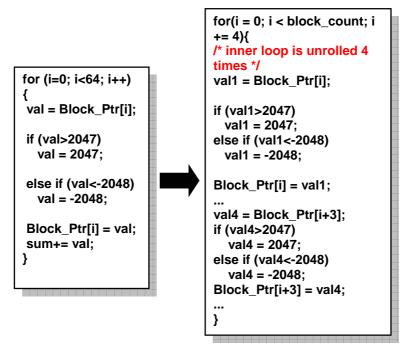

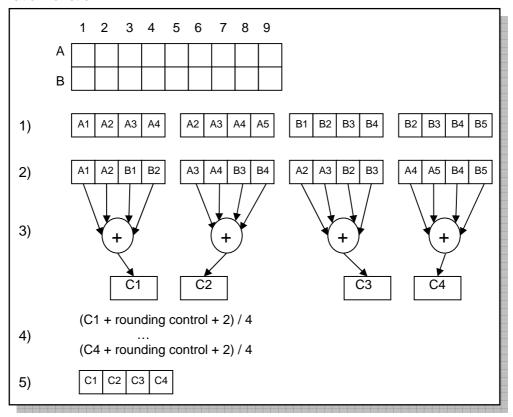

**Loop Unrolling**: The ADRES array is much bigger than other processor architectures. When a loop is mapped to the ADRES array, the loop body should be big enough to efficiently utilize the resources. Considering a loop consisting of only 10 operations, when it is mapped to an 8x8 array the utilization is at most 15.6% (10/64) and instruction-per-cycle is at most 10 if the loop is fully pipelined. One solution to this problem is known as loop unrolling. Generally, loop unrolling is the process of expanding a loop so each new iteration contains several copies of a single iteration. It also adjusts loop termination code and eliminates redundant branch instructions. Traditionally, it is an optimization technique that can reduce the total number of instructions executed by a processor and can increase instruction-level parallelism. Applied to the ADRES architecture, it also helps to increase the size of loop bodies so that pipelining is more efficient on a big array. Figure 12 shows one example. The original loop body is very small and cannot efficiently utilize an ADRES array. After unrolling the loop 4 times, the loop body contains about 4 times more static operations (the number of operations in the compiled code) than the original loop body, while the total number of dynamic operations (the number of operations actually executed) is about the same. Both the original loop and the transformed one can be fully pipelined to achieve 1 cycle/per iteration. Therefore the performance is increased 4 times after loop unrolling.

Figure 12 Example of loop unrolling

Loop unrolling involves a trade-off between the loop body size and the total number of iterations. If the loop is unrolled too many times, the total number of operations will increase undesirably while the performance doesn't increase accordingly. A bigger loop body requires more configuration contexts. At the same time, the total number of iterations will shrink so that the overhead of prologue and epilogue becomes prominent.

Increasing Iterations: Loop coalescing is one way to increase the total number of iterations in order to reduce the prologue and epilogue overhead in nested loops. In fact, increasing the total number of iterations can be very application-specific. If the designer understands the application better, more opportunities may be discovered to increase total number of iterations of a loop. Figure 10 also shows one example of this transformation applied to IDCT. The original loop is based on a basic block (8x8) consisting of only 8 iterations. After transformation, the IDCT loop is performed on a macroblock, which usually contains a number of basic blocks (shown as block count). Hence, the total number of iterations increase to 8 x block count so that the prologue and epilogue overhead is greatly reduced.

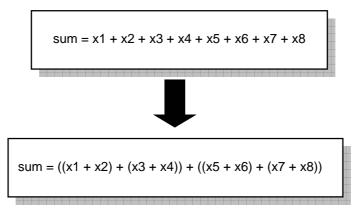

**Tree Height Reduction**: in a pipelined loop, the schedule length determines the total number of pipeline stages. A higher number of pipeline stages has a negative impact on performance due to the increased prologue and epilogue overhead. Sometimes the schedule length can be reduced by a technique known as tree height reduction. Figure 13 describes a simple example. Before and after the transformation the tree heights are

7 and 3 cycles respectively. Though some algorithm was developed to automatically perform this transformation, it can be easily done at source-level by the developer.

Figure 13 Example of tree height reduction

Reducing Memory Access: though the ADRES array has abundant computing resources, it still has resource bottlenecks, especially related to the memory bandwidth. Pipelining usually demands very high memory bandwidth. Consider for example an iteration that contains 10 memory accesses (both reads and writes) and an ADRES instance that has 2 memory ports. In this case, each iteration requires at least 5 cycles to meet the memory bandwidth constraint. For many kernels the memory access bandwidth can be reduced by replacing array variables with scalar ones. In normal processors, the scalar variables are stored in the register file. If there are too many scalar variables, they have to be spilled to the memory in which case the memory access is not eliminated. In the ADRES architecture, the scalar variables are stored in register files distributed throughout the array. These RFs are cheap to use and don't introduce a resource bottleneck for memory access. Normally after transform the code, the memory accesses decrease at the expense of an increased amount of operations. With abundant FUs available in the ADRES array, it is worth to trade memory accesses for more operations if the memory bandwidth is a bottleneck.

#### 3.3 Guidelines for Source-Level Transformations

The required source-level transformations are very diverse and sometimes application-specific. In many cases, several transformations are performed together on one loop. So in this section are given some examples to illustrate the transformations instead of defining formal algorithms for the transformations. While some transformations such as function inlining and tree height reduction are good candidates for future automation, it is very difficult to automate other transformations, especially the application-specific ones.

#### **CHAPTER 3: SOURCE-LEVEL TRANSFORMATIONS**

Currently they are performed manually by the application designer. Nonetheless, it doesn't require a lot of effort to modify a number of loops at source-level for typical applications.

- Remove obstacles of pipelining for the candidate loop.

- Make the candidate loop significant in terms of execution time.

- Transform the candidate loop to have sufficient iterations.

- Balance resource utilization and total number of configuration contexts.

- Reduce memory access if the memory bandwidth is a bottleneck.

- Reduce total number of pipeline stages to minimize prologue/epilogue overhead.

#### Chapter 4

## MPEG-4

As it has already been said, in order to evaluate the capabilities of ADRES an MPEG-4 encoder has been chosen. This chapter tries to give a general overview of the MPEG-4 natural video coding. Some functionalities are described briefly as well as some basic principles of the standard. Additionally the importance of each part in cycles terms is showed. Further information of the specific parts of the MPEG-4 encoder will be explained more accurately in following chapters.

#### 4.1 MPEG-4 standard

ISO/IEC Standard 14496 Part 2 (MPEG-4 Visual [[9,[10]) improves on the popular MPEG-2 standard both in terms of compression efficiency (better compression for the same visual quality) and flexibility (enabling a much wider range of applications). It achieves this in two main ways, by making use of more advanced compression algorithms and by providing an extensive set of 'tools' for coding and manipulating digital media. MPEG-4 Visual consists of a 'core' video encoder/decoder model together with a number of additional coding tools. The core model is based on the well-known hybrid DPCM/DCT (Differential Pulse Code Modulation/Discrete Cosine Transform) coding model (see description section) and the basic function of the core is extended by tools supporting (among other things) enhanced compression efficiency, reliable transmission, coding of separate shapes or 'objects' in a visual scene, mesh-based compression and animation of face or body models.

MPEG-4 Visual attempts to satisfy the requirements of a wide range of visual communication applications through a toolkit-based approach to coding of visual information. Some of the key features that distinguish MPEG-4 Visual from previous visual coding standards include:

- Efficient compression of progressive and interlaced 'natural' video sequences (compression of sequences of rectangular video frames). The core compression tools are based on the ITU-T H.263 standard and can out-perform MPEG-1 and MPEG-2 video compression. Optional additional tools further improve compression efficiency.

- Coding of video objects (irregular-shaped regions of a video scene). This is a new concept for standard-based video coding and enables (for example) independent coding of foreground and background objects in a video scene.

- Support for effective transmission over practical networks. Error resilience tools help a decoder to recover from transmission errors and maintain a successful video connection in an error-prone network environment and scalable coding tools can help to support flexible transmission at a range of coded bitrates.

- Coding of still 'texture' (image data). This means, for example, that still images can be coded and transmitted within the same framework as moving video sequences. Texture coding tools may also be useful in conjunction with animation-based rendering.

- Coding of animated visual objects such as 2D and 3D polygonal meshes, animated faces and animated human bodies.

- Coding for specialist applications such as 'studio' quality video. In this type of application, visual quality is perhaps more important than high compression.

MPEG-4 Visual provides its coding functions through a combination of *tools*, *objects* and *profiles*. A *tool* is a subset of coding functions to support a specific feature (for example, basic video coding, interlaced video, coding object shapes, etc.). An *object* is a video element (e.g. a sequence of rectangular frames, a sequence of arbitrary-shaped regions, a still image) that is coded using one or more tools. For example, a simple video object is coded using a limited subset of tools for rectangular video frame sequences, a core video object is coded using tools for arbitrarily-shaped objects and so on. A *profile* is a set of object types that a CODEC is expected to be capable of handling.

One of the key contributions of MPEG-4Visual is a move away from the 'traditional' view of a video sequence as being merely a collection of rectangular frames of video. Instead, MPEG-4 Visual treats a video sequence as a collection of one or more *video objects*. MPEG-4 Visual defines a video object as a flexible 'entity that a user is allowed to access (seek, browse) and manipulate (cut and paste)'. A video object (VO) is an area of the video scene that may occupy an arbitrarily-shaped region and may exist for an arbitrary length of time. An instance of a VO at a particular point in time is a *video object plane* (VOP).

Notwithstanding the potential flexibility offered by object-based coding, the most popular application of MPEG-4 Visual is to encode complete frames of video. The tools required to handle rectangular VOPs (typically complete video frames) are grouped together in the so-called *simple* profiles. The basic tools are similar to those adopted by previous video coding standards, DCT-based coding of macroblocks with motion compensated prediction. The Simple profile is based around the well-known hybrid DPCM/DCT model (it will be described in the description section) with some additional tools to improve coding efficiency and transmission efficiency. Because of the widespread popularity of Simple profile, enhanced profiles for rectangular VOPs have been developed. The input to an MPEG-4 Visual encoder and the output of a decoder is a video sequence in 4:2:0, 4:2:2 or 4:4:4 progressive or interlaced formats.

#### 4.2 MPEG-4 encoder description

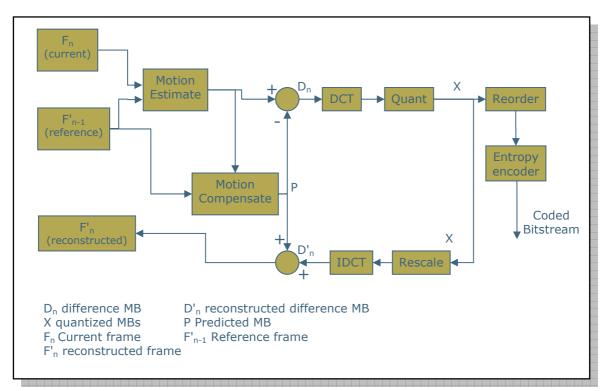

The major video coding standards released since the early 1990s have been based on the same generic design (or model) of a video CODEC that incorporates a motion estimation and compensation front end (sometimes described as DPCM), a transform stage and an entropy encoder. The model is often described as a hybrid DPCM/DCT CODEC. Any CODEC that is compatible with H.261, H.263, MPEG-1, MPEG-2, MPEG-4 Visual and H.264 has to implement a similar set of basic coding and decoding functions (although there are many differences of detail between the standards and between implementations). Figure 14 depicts a generic DPCM/DCT hybrid encoder. In the encoder, video frame n (Fn) is processed to produce a coded (compressed) bitstream.

Figure 14 Encoder data flow

There are two main data flow paths in the encoder, left to right (encoding) and right to left (reconstruction). The encoding flow is as follows:

- An input video frame Fn is presented for encoding and is processed in units of a macroblock (corresponding to a 16 x 16 luma region and associated chroma samples).

- 2. Fn is compared with a reference frame, for example the previous encoded frame  $(F'_{n-1})$ . A motion estimation function finds a 16 × 16 region in  $F'_{n-1}$  (or a subsample interpolated version of  $F'_{n-1}$ ) that 'matches' the current macroblock in Fn

(i.e. is similar according to some matching criteria). The offset between the current macroblock position and the chosen reference region is a motion vector (MV).

- 3. Based on the chosen MV, a motion compensated prediction P is generated (the  $16 \times 16$  region selected by the motion estimator).

- 4. P is subtracted from the current macroblock to produce a residual or difference macroblock D.

- 5. D is transformed using the DCT. Sometimes, D is split into  $8 \times 8$  or  $4 \times 4$  subblocks and each sub-block is transformed separately.

- 6. Each sub-block is quantized (X).

- 7. The DCT coefficients of each sub-block are reordered and run-level coded.

- 8. Finally, the coefficients, motion vector and associated header information for each macroblock are entropy encoded to produce the compressed bitstream.

The reconstruction data flow is as follows:

- 1. Each quantized macroblock X is rescaled and inverse transformed to produce a decoded residual D'. Note that the nonreversible quantization process means that D' is not identical to D (i.e. distortion has been introduced).

- 2. The motion compensated prediction P is added to the residual D' to produce a reconstructed macroblock and the reconstructed macroblocks are saved to produce reconstructed frame F'<sub>n</sub>. After encoding a complete frame, the reconstructed frame F'<sub>n</sub> may be used as a reference frame for the next encoded frame F'<sub>n+1</sub>

Notice that not all the frames follows this process because sometimes it is necessary to send to the decoder all the information frame and not only de difference with the reference frame. Frames that haven not reference frames are called INTRA frames and the others are called INTER frames.

#### 4.3 Code mapped

Before start changing the code it is necessary to analyze the code in order to know where it is necessary to concentrate efforts.

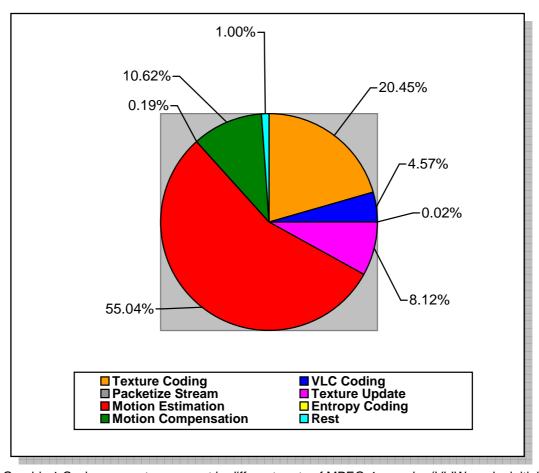

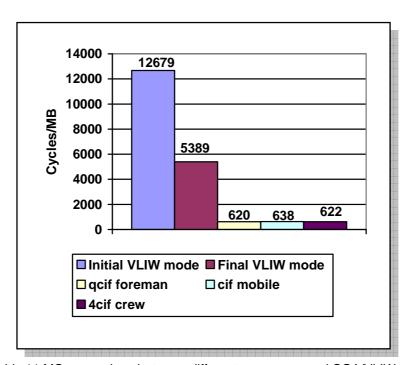

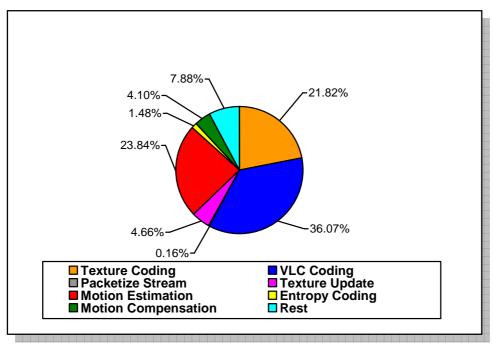

Graphic 1 shows us which parts of an MPEG-4 encoder has more specific weight in terms of cycles. Main parts are Motion Estimation block, where a 55,04% of total cycles are spent, and Texture Coding block with 20,45%. Therefore the main optimizing effort is spent in these 2 blocks.

Additionally Motion Compensation Block and Texture Update Block have rather importance, 10,62% and 8,12% respectively, and for this reason are also mapped.

#### CHAPTER 4: MPEG-4

Hence, code cycles spent in these four parts together are more than 94% of the total amount of cycles in VLIW mode.

Graphic 1 Cycles percentages spent in different parts of MPEG-4 encoder (VLIW mode, initial code)

#### Chapter 5

## **Texture Coding**

#### 5.1 Introduction

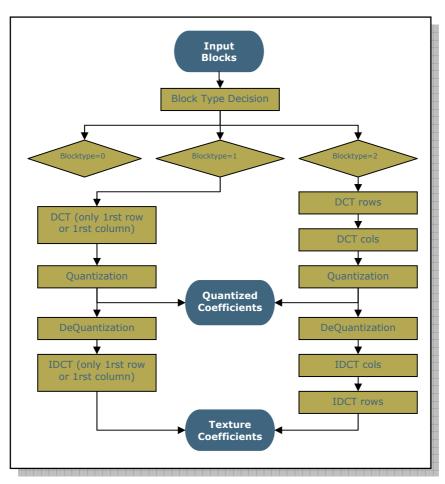

The first step of the TC function consists of choosing the block type:

- Blocktype 0: no computation is made.

- Blocktype 1: only 8 coefficients are computed.

- Blocktype 2: all 64 coefficients are calculated.

By distinguish 3 kind of blocks is possible to avoid calculating unnecessary coefficients. Due to the Discrete Cosine Transform (DCT) a great number of coefficients are 0 or near to 0. Finally, these coefficients can be discarded in the Quantization step.

The selection of the blocktype is carried out calculating with the Sum of Absolute Differences (SAD). The SAD finds the similarity between two macroblocks (MB). A greater similarity between the two matrices results in a smaller SAD value. Depending on his level the block types are chosen. In order to do this 2 thresholds are settled: if the SAD block is minor than the first threshold then the block is type 0 and the next steps are skipped; if the SAD block is between the 2 thresholds then the block is type 1 and only 8 coefficients will be computed; and if the second threshold is surpassed then the next steps will be executed for all 64 coefficients. Therefore, all the blocks in mode INTRA will be type 2.

Once the block type decision has been carried out, the next steps depend on the block type. As the number of iterations is greater when a block is type 2, we focus the optimization in this part of the code.

Figure 15 shows in general terms how Texture Coding function behaves.

As we compute all coefficients when the block is type 2, because the major number of cycles is spent here, but in order to decrease as much as possible the cycles of Texture Coding, the functions in mode 1 are also mapped. These are the functions mapped in CGA:

- DRESC BlockDirDCTQuantH263

- DRESC\_BlockDirDequantH263IDCT

- DRESC DCTrows

- \_DRESC\_DCTcols

- \_DRESC\_Q\_invQ

- \_DRESC\_IDCTcols

- \_DRESC\_IDCTrows

Figure 15 Texture Coding flowchart

To optimize the code 3 main steps are applied. In the first step, the code is modified in order to map into CGA (remove functions calls inside the loops, merging loops...). Once the different functions (DCT\_Rows, DCT\_Cols...) could be mapped, the code is adapted to obtain better results (decrease the number of cycles). Finally the last transformation step is to pass from block level to Macro Block level; the reason is to increase the amount of iterations in each loop. At the end of this process the optimization of kernels for blocks type 1 is performed.

#### 5.2 Block Level

The original code was written in a way that the functions are inside the loop. Therefore, first the code was changed to split the loop in different loops for the different functions, as well to create de quantization-dequantization function (called Q\_invQ).

```

for (rows)

DCTRows

for (columns)

{

DCTCols

for (rows)

Quant/DeQuant

IDCTCols

}

for (rows)

IDCTRows

```

```

for (rows)

DCTRows

for (columns)

DCTCols

for (coefficients)

Quant/DeQuant

for (columns)

IDCTCols

for (rows)

IDCTRows

```

Figure 16 Initial and final schematic block level code

The first 2 functions were basically transformed to enable the mapping in the CGA. Therefore, the functions DCTrows and DCTcols, where a DCT is carried out first for the rows in the block and then for the columns, remained essentially the same as in the original code only changing the pertinent code to avoid function calls inside the loops. These transformations results in the following scheduling characteristics

| Kernel   | NrCycles | SD     | 11 | PS | IPC   | Length |

|----------|----------|--------|----|----|-------|--------|

| DCT_Rows | 107      | 78,47% | 9  | 4  | 12,55 | 34     |

| DCT_Cols | 98       | 76,56% | 8  | 5  | 12,25 | 33     |

Table 1 Scheduling results for DCT

#### 5.2.1 Quantization/DeQuantization function

This function has a higher complexity and many code transformations are applied. As the quantization is different depending on mode of the Macro Block (INTER or INTRA), there were 3 different loops in the original code: one for the INTRA blocks, one for the INTER blocks and the other to reconstruct coefficients.

In INTRA mode, the first coefficient has a special treatment, because it is the DC coefficient. It is quantized as follows:

$$QF[0][0] = \frac{in[0][0] + \frac{dc\_scaler}{2}}{dc\_scaler}$$

Whereas the other coefficients have this other quantization:

$$\left|QF[i][j]\right| = \frac{\left|in[i][j]\right|}{2\cdot Qp}$$

In INTER mode all the coefficients inside the block are quantized in the same way:

$$\left| QF[i][j] \right| = \left| in[i][j] - \frac{Qp}{2} \right| 2 \cdot Qp$$

The formula to reconstruct the coefficients is as follows:

$$|F[i][j]| = \begin{cases} 0 & \text{if } QF[i][j] = 0 \\ (2 \cdot |QF[i][j]| + 1) \cdot Qp & \text{if } QF[i][j] \neq 0 \ Qp & \text{is odd} \\ (2 \cdot |QF[i][j]| + 1) \cdot Qp - 1 & \text{if } QF[i][j] \neq 0 \ Qp & \text{is even} \end{cases}$$

First, a function for the quantization-dequantization was created, (\_DRESC\_Q\_invQ). Once the function was created, there were 4 loops. The Figure 17 shows the loop disposition.

```

for (rows)

for (columns)

INTRA_Quantization

for (columns)

INTER_Quantization

for (columns)

Dequantization

```

Figure 17 DRESC\_Q\_invQ original schematic disposition

Therefore, to able the mapping in CGA, the technique of loop coalescing was applied. Unfortunately the function still had 3 loops, because of the different quantization between modes, and also the last loop to reconstruct the coefficients.

To merge the 2 modes a parameter (called QuantA) was created. It has 2 different values depending on the mode: 0 for mode INTRA and -Qp/2 for mode INTER. In addition, another parameter to select the sign of the quantized coefficients is created. At this point, to merge the loops 2 possibilities were tested:

- 1. Calculate the 64 coefficients and in INTRA mode recalculate the DC coefficient afterwards.

- 2. Calculate the first coefficient depending on the mode and choose the value of QuantA, and then calculate the 63 remaining coefficients.

Finally it's easy to put the code to reconstruct the coefficients at the end of the loop.

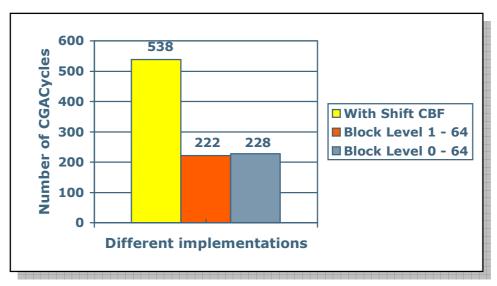

Graphic 2 Q\_invQ implementation results

Graphic 2 shows the different results. First results are so worst because of a high dependency with the variable CBF. CBF indicates in which columns must be applied the IDCT, by setting to one the correspondent bit per column. As the code was changed this shift operation was removed and the number of cycles decreased dramatically.

The graph also shows that the first option (to calculate all the coefficients and then recalculate DC if block is mode INTRA) was worse than the second. Apparently this is logical because in this option the first coefficient is evaluated twice.

There is the possibility to unroll the loop in the first option, to try to decrease the CGA Cycles, unfortunately this option was tried but the CGA couldn't map, because of the architecture resources.

The Table 2 shows the scheduling results for the 2 options tested.

| Kernel<br>Option | NrCycles | SD     | 11 | PS | IPC   | Length |

|------------------|----------|--------|----|----|-------|--------|

| 1st Option       | 228      | 85,42% | 3  | 11 | 13,67 | 36     |

| 2n Option        | 222      | 77,08% | 3  | 11 | 12,33 | 29     |

Table 2 Scheduling results for different Q\_invQ options

#### **5.2.2** IDCT\_cols function

This function already existed in the original code but there was a function call inside. So the first step is to put the main loop inside the function and change the function call by pasting the function code. Then some if statements that only adds overhead were removed.

At this point 2 options were tested:

- 1. Maintaining if CBF conditions.

- 2. Removing if CBF conditions.

CBF was used to know if the IDCT has to be applied in the block or not, on one hand the amount of iterations was reduced, but on the other hand this added more dependencies that means more cycles.

With the CBF condition it was possible to skip a block and only the IDCT is applied if the MB is mode INTRA.

The number of CGA cycles is the same for the 2 options because if statements are outside the loop, but the total cycles are different in the options. Whereas for with if conditions the number of cycles are 262.806 that means an average of 92,43 cycles/block without this conditions the total number of cycles is 292.562 an the average is 104 cycles/block.

| Kernel    | NrCycles | SD     | II | PS | IPC   | Length |

|-----------|----------|--------|----|----|-------|--------|

| IDCT_cols | 88       | 79,46% | 7  | 5  | 12,71 | 31     |

Table 3 IDCT\_cols scheduling results

### **5.2.3** IDCT\_rows function

Like in the other functions there was a function call inside the loop that was removed and replaced for code. Then 2 options were tested as there was also the clipping inside the same loop, it was tested the possibility to split the loop in 2 loops (one for the IDCT and the other for the clipping) but finally the results were worst if the loop was split. shows the scheduling characteristics for these 2 options:

| Kernel Option | NrCycles | SD     | II | PS | IPC   | Length |

|---------------|----------|--------|----|----|-------|--------|

| 1IDCT+CLIP    | 122      | 82,39% | 11 | 3  | 13,18 | 33     |

| IDCT          | 99       | 72,92% | 9  | 3  | 11,66 | 27     |

| CLIP          | 68       | 69,79% | 6  | 4  | 11,16 | 20     |

| Total CLIP + IDCT | 167                                 |

|-------------------|-------------------------------------|

| Т                 | able 4 IDCT_rows scheduling results |

### 5.3 MacroBlock Level

The idea of going to MacroBlock level is to increase the amount of iterations to reduce the "length effect" that means a decrease in the number of cycles.

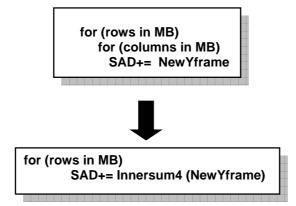

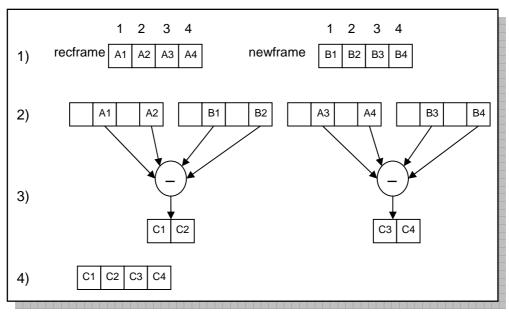

In the original code, the TextureCoding function was running inside a loop for each block. Therefore the function was called 6 times in a MB and each time the function went over rows, columns... The transformation consisted in coalescing the main loop with the smaller function loops (Figure 18).

However the different block types were an issue. The solution consisted in create 3 arrays (for each type of block) where the number of block in the MB was stored in order to compute the correct number of coefficients for each block. Then the coalescing technique was applied.

```

for (blocks)

ModeDecision;

for (blocksmode2 in MB)

DCTrows;

for (blocksmode2 in MB)

DCTcols;

for (blocksmode2 in MB)

Quantization;

for (blocksmode2 in MB)

IDCTcols;

for (blocksmode2 in MB)

IDCTrows;

```

```

for (rows)

DCTRows

for (columns)

DCTCols

for (coefficients)

Quant/DeQuant

for (columns)

IDCTCols

for (rows)

IDCTRows

```

Figure 18 Schematic code in block and macroblock level

Another problem was that in MB level there were more reads at memory than in the block level because it is necessary to store the data in buffers between the different functions. Initially the data was written in the correct position in the MB and then it was changed by writing in consecutive form, and only wrote correctly the TC outputs (Quantized coefficients and reconstructed coefficients), but not the intermediate buffers employed. In this way the total number of reads at memory decreases.

```

Input=inputMB[mode2[k]];

Output=outputMB[mode2[k]] + 8*i;

Output=outputMB[j] +i;

```

Figure 19 Changes in memory accesses

Where mode2[k] is the array which indicates block position in MB and i and j are used to access the different coefficients. What this means is that firstly the outputs were in the correct way but then it was changed to write consecutively.

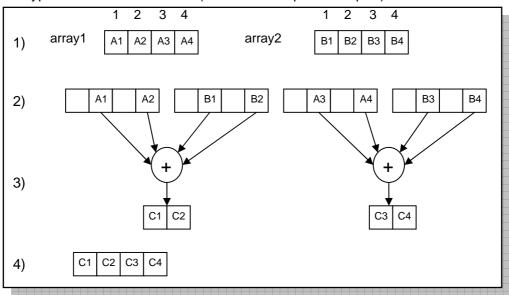

Another way was tried but with worst results. To carry out the DCT and IDCT (over rows and columns), it is necessary to compute 8 coefficients in each iteration, that means 8 reads to the memory. To avoid this, instead of reading 8 times 16 bits (short type), the memory was read 4 times as integer type (32 bits) and then make shifts to store the correct value in the scalar variables. In this way the code had 10 cycles more per block.

```

In=errorMB[mode2[j]] + 8*i;

X6 = In[0];

X1 = In[1];

X3 = In[2];

X8 = In[3];

X4 = In[4];

X5 = In[5];

X2 = In[6];

X7 = In[7];

```

```

In=errorMB[mode2[j]] + 8*i;

In0 = *(int*) (in);

In1 = *(int*) (in+2);

In2 = *(int*) (in+4);

In3 = *(int*) (in+6);

X6 = (short) (in0);

X1 = (short) (in0 >> 16);

X3 = (short) (in1);

X8 = (short) (in1) >> 16);

X4 = (short) (in2);

X5 = (short) (in2 >> 16);

X2 = (short) (in3);

X7 = (short) (in3 >> 16);

```

Figure 20 Different options to read from the memory: short type (left) or integer type (right)

Where In is a pointer, X1...X7 are short scalars and In0...In3 are integer scalars. There was another issue with CBF condition. A buffer was needed to store the value of CBF for each block; as a result of this the number of reads at memory was high.

| DCT_Rows tested   | NrCycles<br>average <sup>1</sup> | SD     | 11 | PS | IPC   | Length |

|-------------------|----------------------------------|--------|----|----|-------|--------|

| Changing buffer   | 82,79                            | 76,56% | 8  | 7  | 12,25 | 43     |

| Normal read/write | 101,36                           | 82,5%  | 10 | 5  | 13,2  | 49     |

Table 5 Scheduling results for different options to read at memory

<sup>&</sup>lt;sup>1</sup> Cycles average depends on the number of blocks type 2 in a MB. All statistics are taken with a 300 frames quif foreman sequence.

There are 2 things which are necessary to indicate. Firstly the number of cycles is an average because sometimes the number of iterations in the function is different. This is due to the different number of blocks in mode 2 in the MB. The second thing is that the II is reduced from 10 to 8, and in the block level it was 9. Therefore, this is an important point to be considered in future. In DCT\_cols function happens the same. The reduction of load/store at memory allows to decrease the II and of course the number of cycles.

|          | NrCycles<br>average | SD     | 11 | PS | IPC   | Length |

|----------|---------------------|--------|----|----|-------|--------|

| DCT_cols | 79,80               | 73,44% | 8  | 5  | 11.75 | 36     |

Table 6 Scheduling results for DCT\_Cols in MB level

In Quantization/DeQuantization function, the problematic with accessing to the memory was more visible because of the number of iterations is higher, 64\*Nrblocks instead of 8\*Nrblocks, in the other functions.

The clipping in this function and in IDCT\_Rows functions, are different from the available intrinsic clipping functions. Therefore a new function was created. The reason is that the previously created intrinsic functions make the clipping as follows:

$$-MaxVal \le Value \le Maxval$$

$0 \le Value \le Maxval$

Whereas in the code has to be:

$$-MaxVal - 1 \le Value \le Maxval$$

$1 \le Value \le Maxval$

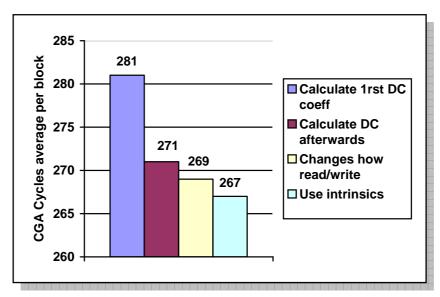

Once the function was mapped in MB level some transformations were made. Firstly the order of calculations is reverted to 1rst option, that means to calculate the 64 coefficients for all blocks and then, if it was necessary, the DC coefficients for INTRA mode blocks. Therefore there are 2 loops in the function. It wasn't necessary another loop to know the value of parameter QuantA because all blocks in the same MB are in the same mode.

As it was necessary to write the quantized coefficients in the correct block, the pass of *mode2* array, which indicates the position, was a ballast to decrease the cycles. In addition, the CBF parameter is transformed to an array, which means more accesses to the memory and more cycles.

Finally with the use of intrinsics the number of cycles decreased but not enough to reach the block level results.

Graphic 3 Q\_invQ Implementations in MB Level

| Quantization using intrinsics | NrCycles average | SD     | 11 | PS | IPC  | Length |

|-------------------------------|------------------|--------|----|----|------|--------|

| 64 loop                       | 265,79           | 75%    | 4  | 8  | 12   | 30     |

| DC coeff loop                 | 1,26             | 65,62% | 2  | 12 | 10,5 | 23     |

| Total                         | 267,06           |        |    |    |      |        |

Table 7 Q\_invQ scheduling results in Mb level

In the IDCT\_Cols function the effect of changing the way to access at memory was so important and the number of iterations decreased dramatically. To carry out these accesses, the if CBF conditions were removed. This couldn't be possible in the IDCT\_Rows function.

| IDCT_Cols             | NrCycles average | SD     | 11 | PS | IPC   | Length |

|-----------------------|------------------|--------|----|----|-------|--------|

| With CBF conditions   | 100              | 64,77% | 11 | 4  | 10,36 |        |

| Changing reads/writes | 65,08            | 86,46% | 6  | 7  | 13,83 | 39     |

Table 8 Different scheduling results for IDCT\_Cols in MB level

In IDCT\_Rows function it wasn't possible to avoid the CBF condition outside the function. In order to know which blocks have to be computed it was created another loop before the function. In this loop was stored the position of the block in a new array if the CBF of

this block was 1. This is the reason because it wasn't possible to decrease so much the number of cycles, as the input needs to know the position of block and the output must be correct.

|           | NrCycles average | SD     | 11 | PS | IPC  | Length |

|-----------|------------------|--------|----|----|------|--------|

| IDCT_Rows | 86,86            | 84,38% | 8  | 6  | 13,5 | 45     |

Table 9 IDCT\_Rows scheduling results obtained in MB level

### 5.4 Block Type 1

Although in this mode there are only 2 functions to map in the CGA (BlockDirDCT-QuantH263 and BlockDirDequantH263IDCT), inside of this functions there were several loops. These 2 functions make all the computation for 8 coefficients. The first function choose in which direction has to make the computation (compares adds of rows versus columns and the highest is chosen), and then makes DCT for this 8 coefficients and the quantization. The second function makes inverse process. Firstly makes the dequantization, then the IDCT and finally stores the results.

To be able the mapping in CGA some transformations in the code were made. Firstly splitting the main loop and pasting the function code inside. Then, the coalescing of loops and some variable transformations (in order to maintain the code functionality and to avoid some unnecessary accesses at memory) were made. Finally the clipping intrinsic function was added.

| BlockDirDCTQuantH263      | NrCycles<br>average | SD     | 11 | PS | IPC   | Length |

|---------------------------|---------------------|--------|----|----|-------|--------|

| Adding Rows & Cols        | 95,64               | 83,04% | 7  | 5  | 13,28 | 32     |

| Tmp_DC                    | 78,29               | 82,81% | 4  | 6  | 13,25 | 23     |

| <b>Choosing direction</b> | 48,51               | 59,34% | 4  | 8  | 9,5   | 30     |

| DCT                       | 53,32               | 71,63% | 13 | 4  | 11,46 | 43     |

| Quantization              | 45,26               | 57,81% | 4  | 7  | 9,25  | 27     |

Table 10 BlockDirDCTQuantH263 scheduling results

| BlockDirDequantH263IDCT | NrCycles<br>average | SD     | II | PS | IPC   | Length |

|-------------------------|---------------------|--------|----|----|-------|--------|

| Dequantization          | 62,93               | 75%    | 3  | 12 | 12    | 36     |

| IDCT                    | 21,26               | 78,13% | 2  | 13 | 12,5  | 27     |

| Write coefficients      | 73,45               | 83,33% | 6  | 6  | 13,33 | 36     |

Table 11 BlockDirDequantH263IDCT scheduling results

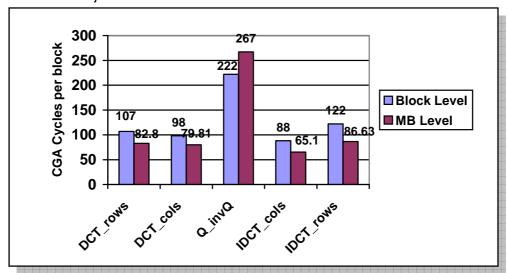

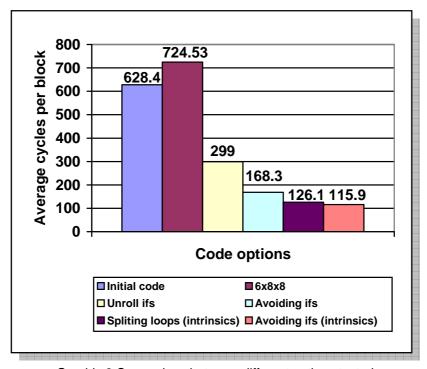

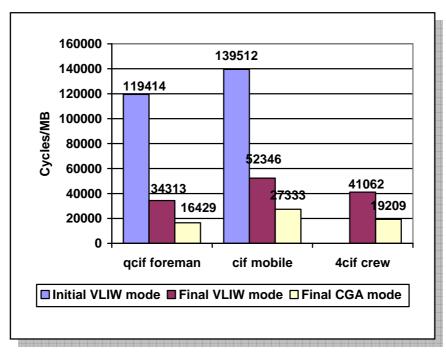

### 5.5 Comparison between block and MB levels

As the graphic shows in all functions, except in Quantization, the results were better because of the major number of iterations.

Graphic 4 CGA Cycles comparison between block and MB levels

|                                                  | Block   | Final          |

|--------------------------------------------------|---------|----------------|